Shakti – C Class Processor

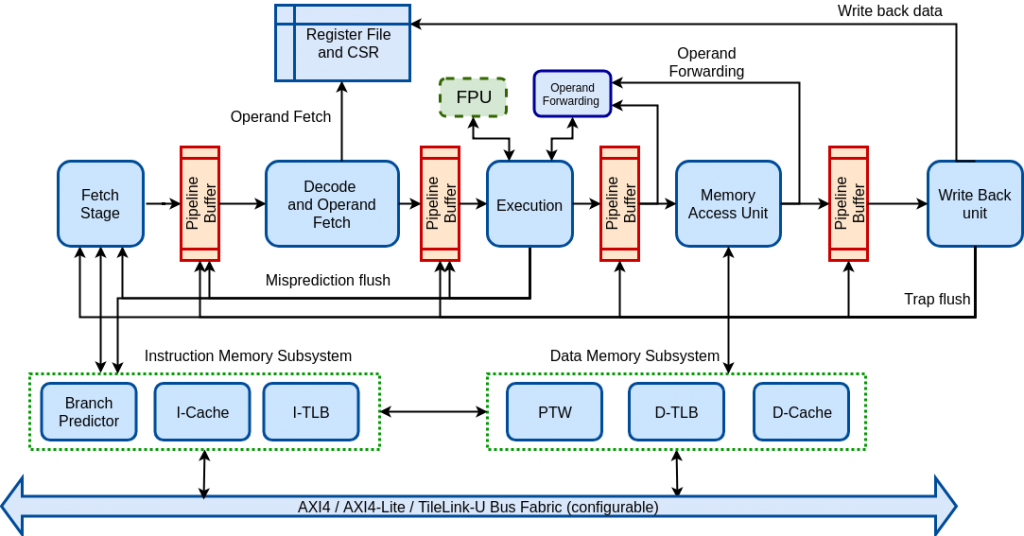

C Class : The C Class is a controller class of processors, aimed at mid-range application workloads. The core is a highly optimized, 5-stage in-order design with MMU support and capability to run operating systems Linux and Sel4. These processors are targeted at compute/control applications in the 0.5-1.5 Ghz range. The C-class will supports the full RISC-V ISA. The C Class is also the basis for our Tagged-ISA and Fault tolerant cores.

Architectural Features

Overview :

- An in-order 5-stage 64-bit microcontroller supporting the entire stable RISC-V ISA.

- Targets mid-range compute systems: 200-800MHz (can be customized for 2 Ghz applications)

- Supports RISC-V Linux, secure L4

- Variants for low-power and high-performance.

- Positioned against ARM’s Cortex A35/A55.

Basic Specifications

- Supports RISC-V ISA: RV64IMAFD.

- Compatible with latest privilege spec (v1.10) of RISC-V ISA and supports the sv39/48 virtualization scheme.

- Single and Double Precision Floating point units compliant with IEEE-754.

- Supports the OpenOCD based debug environment through JTAG.

- Includes a High performance branch predictor with a Return-Address-Stack.

- Caches: 16-64KB non-blocking pipelined Instruction and Data caches. Optional L2.

- Includes operand forwarding scheme for better performance.

- Boots RISC-V Linux.